## Smart Metering: Entwicklung eines intelligenten Stromzählers

Boppard, Echtzeit 2010

Steffen Mauch Dirk Benyoucef

# Gliederung

- 1 Kontext

- 2 Arbeit

- 3 Ergebnisse / Bewertung

- 4 Zusammenfassung

# Gliederung

- 1 Kontext

- 2 Arbeit

- 3 Ergebnisse / Bewertung

- 4 Zusammenfassung

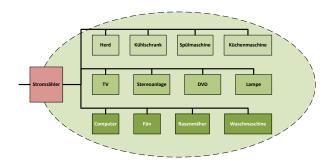

# **Smart Metering**

## Forschungsvorhabens

Ziel des Forschungsvorhabens 'Smart Metering: Disaggregation von Endverbraucher' ist die Identifikation der Verbraucher durch Beobachtung des Energieverbrauchs am Energiezähler.

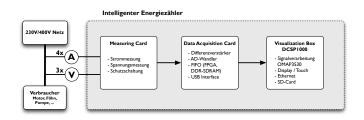

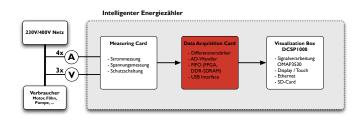

## Der intelligenter Stromzähler

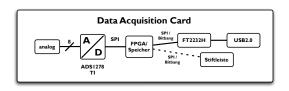

### Messsystem

### Das System besteht aus den Komponenten

- ► Measuring Card,

- Data Acquisition Card und

- Visualization Box.

## Der intelligenter Stromzähler

### Messsystem

### Das System besteht aus den Komponenten

- ► Measuring Card,

- Data Acquisition Card und

- Visualization Box.

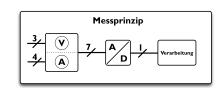

# Der intelligenter Stromzähler

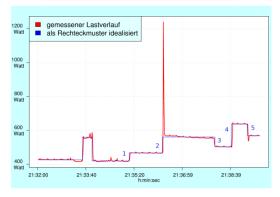

# Messprinzip

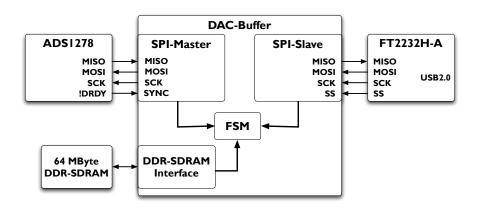

#### Technische Daten

- 8 parallele differentielle Eingangskanäle

- 24 Bit A/D-Wandler (ADS1278 von TI)

- max. Abtastfrequenz 125 kHz

- Spartan 3E FPGA XC3S500E-4FG320C

- 64 MByte DDR-SDRAM

- USB-Schnittstelle mittels FT2232H

## **Problemstellung**

#### Ziele

Sicherer Datentransfer von DAC  $\rightarrow$  PC möglichst in Echtzeit über USB oder Ethernet

- Datenvolumen bis 24 MBit/s

- kein Verlust von Daten

- Konfiguration des AD-Wandlers per USB

- optional Ethernet

#### Problem

USB ist nur eingeschränkt echtzeitfähig!

# Gliederung

- 1 Kontext

- 2 Arbeit

- DDR-Core Konzept

- MicroBlaze Konzept

- 3 Ergebnisse / Bewertung

- 4 Zusammenfassung

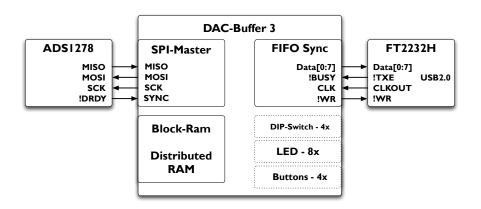

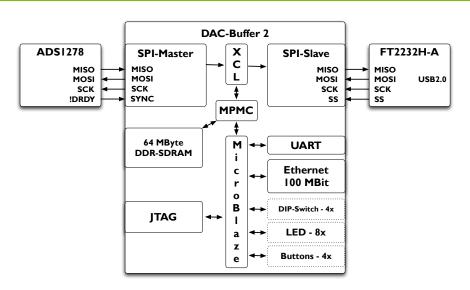

# **DAC-Buffer Konzept**

- 1. Konzept DDR-Core SPI

- 2. Konzept DDR-Core FIFO sync

- 3. Konzept MicroBlaze

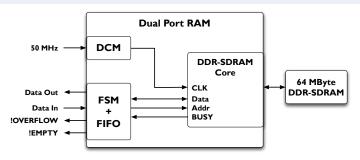

## **SPI DDR-Core Konzept**

### **Dual Port Interface**

#### **Problem**

Der Speichercontroller in VHDL ist nicht Dual Port fähig.

# Lösung

Takt wird durch die DCM des FPGA verdoppelt. SPI-Master und -Slave können nun 'gleichzeitig' zugreifen.

## **FIFO DDR-Core Konzept**

## Bewertung des DDR-Core Konzept

#### Vorteile

- Einfache Realisierung

- Geringe Anforderungen an den FPGA

### Nachteile

- aufwendig bei Erweiterungen

- keine einfache Integration von Ethernet möglich

#### Was ist der MicroBlaze?

#### Merkmale

- 32-bit RISC Microcontroller für FPGAs von Xilinx

- keine physischer μC sondern ein Softcore

- 3- bis 5-stufige Pipeline, interner Cache, PLB und OPB Bus, ...

- umfangreiche IP Module

- Betriebssysteme: μClinux, Linux oder FreeRTOS

#### Vorteile von MicroBlaze

#### Vorteile

- MPMC Anbindung durch PLB Bus

- OPB Bus für Peripherie

- z.B. Integration von Ethernet

- sehr leistungsstark und relativ leicht modifizierbar

### Nachteil

- größerer Overhead für Projektstart

- viele vordefinierte Schnittstellen (Spezifikationen)

- komplexe Struktur

- aufwendige Fehlersuche

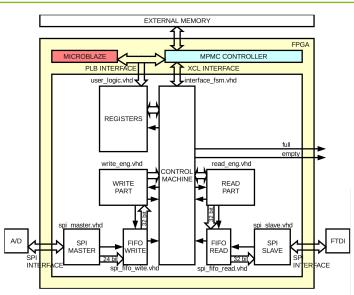

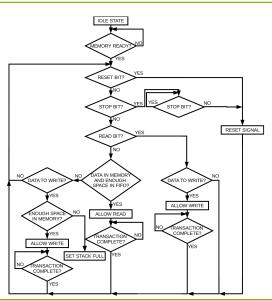

## MicroBlaze Konzept

#### control FSM

# Gliederung

- 1 Kontext

- 2 Arbeit

- 3 Ergebnisse / Bewertung

- Benchmark

- 4 Zusammenfassung

#### **Benchmark**

#### Software

- libFTDI mit asynchroner Programmierung (SPI, FIFO-Modus)

- Qt4-Core für die Threads und Dateiverwaltung

- MySQL Datenbankanbindung

- Scope f

ür graphische Visualisierung

```

2 «TNFO»

<cords

<version>rev.1

cbuild-datesWednesday, 17.November 2010 - 22:32:50 Uhrs/build-dates

<day>2010-11-17</day>

18

<time>22:32:51</time>

11

12 </INFO>

13 <DATA>

<blocks

<ch1>0.000000000</ch1>

<ch2>-3,30000000</ch2>

<ch3>3,30000000e/ch3>

sch4>0.00000000c/ch4>

<ch5>-2.50000000</ch5>

cch6x2 50000000c/ch6x

<ch7>0.00000000</ch7>

<ch8>0.000000004/ch8>

<ch1>0.84147098</ch1>

<ch2>-3.30000000</ch2>

<ch3>3,30000000e/ch3>

<ch4>0.000000000-/ch4>

<ch5>-2.50000000<c/ch5>

cchfo2.50000000c/chfo

rch7x0_000000000/ch7x

<ch8>0.00000000</ch8>

```

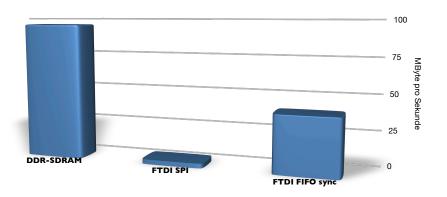

### **Benchmark - Datenrate**

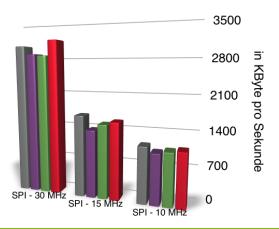

### **Benchmark - SPI**

■ Mac OS X 10.5■ Linux Ubuntu 9.04■ Beagleboard■ Linux Debian 4.0

# Gliederung

- 1 Kontext

- 2 Arbeit

- 3 Ergebnisse / Bewertung

- 4 Zusammenfassung

- 1. kontinuierliche hochgenaue Datenerfassung

- 2. echt parallele Abtastung

- 3. Echtzeit Datenerfassung

- Testen auf dem Xilinx Evalboard

- 5. Entwicklung eines kompakten DAC-Boards

- 1. kontinuierliche hochgenaue Datenerfassung

- 2. echt parallele Abtastung

- Echtzeit Datenerfassung

- Testen auf dem Xilinx Evalboard

- 5. Entwicklung eines kompakten DAC-Boards

- 1. C kontinuierliche hochgenaue Datenerfassung

- 2. echt parallele Abtastung

- 3. Echtzeit Datenerfassung

- Testen auf dem Xilinx Evalboard

- Entwicklung eines kompakten DAC-Boards

- 1. kontinuierliche hochgenaue Datenerfassung

- 2. echt parallele Abtastung

- 3. Centzeit Datenerfassung

- 4. Testen auf dem Xilinx Evalboard

- Entwicklung eines kompakten DAC-Boards

- 1. kontinuierliche hochgenaue Datenerfassung

- 2. echt parallele Abtastung

- 3. Chtzeit Datenerfassung

- 4. Testen auf dem Xilinx Evalboard

- 5. Entwicklung eines kompakten DAC-Boards

#### **Ausblick**

- Einbindung des FIFO-Sync Modus an XCL-FSM

- Downsampling bzw. Datenverarbeitung im FPGA

- Ethernetstream per Linux (UDP, TCP/IP)

- A/D-Wandler wechseln für z.B. Logic Analyser

- Fehlerkorrigierender Code für Datenübertragung an Computer

### Vielen Dank für Ihre Aufmerksamkeit.